Vol. No.7 Issue 02, July-December 2015

www.arresearchpublication.com

# DTMF BASED INDUSTRIAL AUTOMATION

# Shobhnendra Kumar<sup>1</sup>, Shrishti Srivastava<sup>2</sup>, Pallavi Gupta<sup>3</sup>

<sup>1, 2</sup>Students, Electrical Engineering Department, Greater Noida Institutes of Technology, Gr.Noida, (India)

#### **ABSTRACT**

The proposed project is based on the concept of Industrial automation. In this project, we are going to develop a project basically dependent on DTMF, Microcontroller & relay etc. The system allows complete security and is based on microcontroller. The design objective of this project is to make a DTMF based remote monitoring system which can be used to acquire different parameters of any process or machine and send the data obtained to a distant logging system running on a PC so that the data can be represented in a user friendly manner. Here microcontroller is the most important part of this project as it plays the most vital role. Firstly the power supply of 5v DC is very essential for this set up, this power supply trigger the microcontroller 8051, then 8051 is directly connected with LCD & device control, LCD gives the info regarding devices that can be operated by microcontroller 8051 & device control here acting as a switch with the help of relays.

Keyword: DTMF, Industrial automation, LCD, Microcontroller, Relay.

## I. INTRODUCTION

Industrial automation is a part of automation which is applied for the ease ,comfort and security of its parts. Many techniques are used in industrial automation such as plant and machine control, control of window shutter, security and surveillance system etc.

Automation are also used in home automation, additional functions in home automation include the control of multi-media home entertainment systems. In this project the industrial automation, is controlled by a mobile phone that makes call to the mobile phone attached to the industrial automation in the course of the call, if any button is pressed control corresponding to the button pressed is heard at the other end of the call. This tone is called dual tone multi frequency tome (DTMF) industrial automation receives this DTMF tone with the help of phone stacked in the industrial automation. The received tone is processed by the DTMF decoder LM8870.

The tone and assignment in DTMF system is shown below:

| frequencies | 1209 hz | 1336 hz | 1477 hz | 1633 hz |

|-------------|---------|---------|---------|---------|

| 697hz       | 1       | 2       | 3       | a       |

| 770hz       | 4       | 5       | 6       | b       |

| 852hz       | 7       | 8       | 9       | С       |

| 941hz       | *       | 0       | #       | d       |

<sup>&</sup>lt;sup>3</sup> Assistant Professor, Electrical Engineering Department, Greater Noida Institutes of Technology, Gr. Noida, (India)

Vol. No.7 Issue 02, July-December 2015

www.arresearchpublication.com

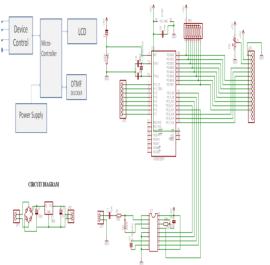

Figure(1): Block Digram & Circuit Diagram

decodes the DTMF tone in to its equivalent binary digit and this binary number is send to the IC 89S51, the IC 89S51 to take a decision for any give input and outputs .DTMF signaling is used for telephone signaling over the line in the voice frequency band to the call switching center. The version of DTMF used for telephone dialing is known as touch tone. DTMF assigns a specific frequency (consisting of two separate tones) to each key s that it can easily be identified by the electronic circuit. The signal generated by the DTMF encoder is the direct al-gerbil submission, in real time of the amplitudes of two sine (cosine) waves of different frequencies, i.e., pressing 5 will send a tone made by adding 1336 Hz and 770 Hz to the other end of the mobile. Although the original DTMF keypad had an additional column for four now-defunct menu selector keys. When used to dial a telephone number, pressing a single key will produce a pitch consisting of two simultaneous pure tone sinusoidal frequencies. The row in which the key appears determines the *low* frequency, and the column determines the *high* frequency. For example, pressing the '1' key will result in a sound composed of both a 697 and a 1209 hertz (Hz) tone. The original keypads had levers inside, so each button activated two contacts. The multiple tones are the reason for calling the system multi frequency. These tones are then decoded by the switching center to determine which key was pressed.

## II. CIRCUIT DIAGRAM

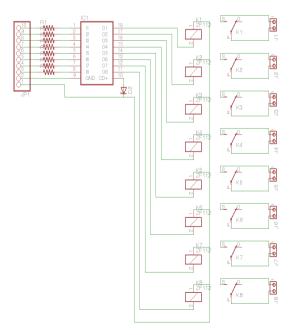

Figure (2): Circuit Diagram

Vol. No.7 Issue 02, July-December 2015

# www.arresearchpublication.com

# III. MICRO CONTROLLER

#### 3.1 Features

- Three-Level Program Memory Lock

- 128 x 8-Bit Internal RAM

- 32 Programmable I/O Lines

- Two 16-Bit Timer/Counters

- Six Interrupt Sources

- Programmable Serial ChannelPin

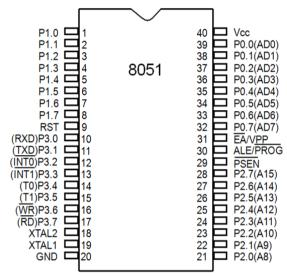

Figure(3):Pin diagram of micro controller

The AT89S51 provides the following standard features: 4K bytes of Flash, 128 bytes of RAM, 32 I/O lines, two 16-bit timer/counters, a five vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator and clock circuitry.

## Port 0:

Port 0 is an 8-bit open drain bidirectional I/O port. As an output port each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as highimpedance inputs. Port 0 may also be configured to be the multiplexed loworder address/data bus during accesses to external program and data memory.

#### Port 1:

Port 1 is an 8-bit bidirectional I/O port with internal pullups. The Port 1 output buffers can sink/source four TTL inputs. When 1s are written to Port 1 pins they are pulled high by the internal pullups and can be used as inputs.

#### Port 2:

Port 2 is an 8-bit bidirectional I/O port with internal pullups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pullups.Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.

**Port 3:** Port 3 is an 8-bit bidirectional I/O port with internal pullups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (IIL) because of the pullups. Port 3 also serves the functions of various special features of the AT89S51 as listed below:

## 3.2 Port Pin Alternate Functions

P3.0 RXD (serial input port)

P3.1 TXD (serial output port)

Vol. No.7 Issue 02, July-December 2015

# www.arresearchpublication.com

P3.2 INT0 (external interrupt 0)

P3.3 INT1 (external interrupt 1)

P3.4 T0 (timer 0 external input)

P3.5 T1 (timer 1 external input)

P3.6 WR (external data memory write strobe)

P3.7 RD (external data memory read strobe

Port 3 also receives some control signals for Flash programming and verification.

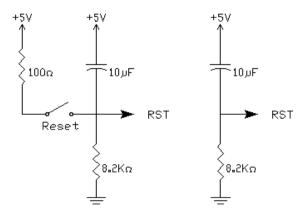

#### RST:

Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device.

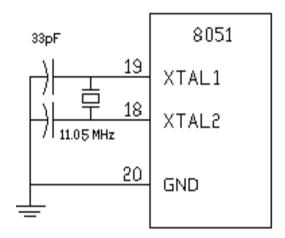

Figure(4): Crystal Oscillator

**Reset Circuit:**RESET is an active High input When RESET is set to High, 8051 goes back to the power on state. The 8051 is reset by holding the RST high for at least two machine cycles and then returning it low.

#### 3.3 Power-On Reset

Initially charging of capacitor makes RST High - When capacitor charges fully it blocks DC.

## 3.4 Manual

Closing the switch momentarily will make RST High. After a reset, the program counter is loaded with 0000H but the content of on-chip RAM is not affected.

Figure (5.1,2) Manual Reset & Power on Reset

Vol. No.7 Issue 02, July-December 2015

www.arresearchpublication.com

| 4 | RAM        | <b>↓</b> 128 BYTES      |  |

|---|------------|-------------------------|--|

| - |            |                         |  |

| + | ROM        | <b>↓</b> 4K             |  |

| 4 | TIMERS     | <b>↓</b> TIMER-0 &      |  |

|   |            | TIMER-1                 |  |

| + |            | ♣   6-INTERRUPT         |  |

| 4 |            | <b>♣</b> 2 INTERRUPTS-  |  |

| 4 |            | EXTERNAL                |  |

| 4 |            | <b>↓</b> 2 INTERRUPTS − |  |

| 4 | INTERRUPTS | TIMER                   |  |

|   |            | <b>↓</b> 1 INTERRUPT –  |  |

|   |            | RESET                   |  |

|   |            | <b>↓</b> 1 INTERRUPT –  |  |

|   |            | SERIAL PORT             |  |

|   |            |                         |  |

|   |            |                         |  |

Pin diagram for 7805

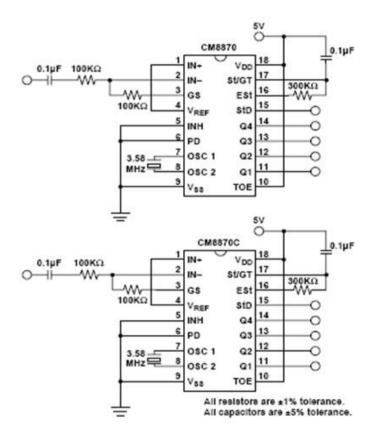

Figure 1. Single ended input configuration

Vol. No.7 Issue 02, July-December 2015

# www.arresearchpublication.com

## **Pin Functions**

| Pin   | Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                      |  |

|-------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| 1     | IN+               | Non-inverting input                                                                                                                                                                                                                                                                                                                                                                                                       | Connections to the front-end differential amplifier.                                 |  |

| 2     | IN-               | Inverting input                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                      |  |

| 3     | GS                | Gain select. Gives access to output of front-end amplifier for connection of feedback resistor.                                                                                                                                                                                                                                                                                                                           |                                                                                      |  |

| 4     | $V_{REF}$         | Reference voltage output (nominally VDD/2). Way be used to bias the inputs at mid-rail.                                                                                                                                                                                                                                                                                                                                   |                                                                                      |  |

| 5     | INH*              | Inhibits detection of tones representing keys A, B, C, and D.                                                                                                                                                                                                                                                                                                                                                             |                                                                                      |  |

| 6     | PD*               | Power down. Logic high powers down the device and inhibits the oscillator. Internal pulldown.                                                                                                                                                                                                                                                                                                                             |                                                                                      |  |

| 7     | OSC1              | Clock input                                                                                                                                                                                                                                                                                                                                                                                                               | 3.579545 MHz crystal connected between these pins completes the internal oscillator. |  |

| 8     | OSC2              | Clock output                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                      |  |

| 9     | VSS               | Negative power supply (normally connected to 0 V).                                                                                                                                                                                                                                                                                                                                                                        |                                                                                      |  |

| 10    | 0E                | Tri-statable output enable (input). Logic high enables the outputs Q1 - Q4. Internal pullup.                                                                                                                                                                                                                                                                                                                              |                                                                                      |  |

| 11-14 | Q1, Q2,<br>Q3, Q4 | Tri-statable data outputs. When enabled by OE, provides the code corresponding to the last valid tone pair received (see Tone Decoding table on page 5).                                                                                                                                                                                                                                                                  |                                                                                      |  |

| 15    | StD               | Delayed steering output. Presents a logic high when a received tone pair has been registered and the output latch is updated. Returns to logic low when the voltage on SUGT falls below VTSL.                                                                                                                                                                                                                             |                                                                                      |  |

| 16    | ESt               | Early steering output. Presents a logic high immediately when the digital algorithm detects a recognizable tone pair (signal condition). Any momentary loss of signal condition will cause ESt to return to a logic low.                                                                                                                                                                                                  |                                                                                      |  |

| 17    | St/GT             | Steering irput/guard time output (bidirectional). A voltage greater than VTSt detected at St causes the device to register the detected tone pair and update the output latch. A voltage less than VTSt frees the device to accept a new tone pair. The GT output acts to reset the external steering time constant, and its state is a function of ESt and the voltage on St. (See Common Crystal Connection on page 5). |                                                                                      |  |

| 18    | V <sub>DD</sub>   | Positive power supply. (Normally connected to +5V.)                                                                                                                                                                                                                                                                                                                                                                       |                                                                                      |  |

## IV. POSITIVE VOLTAGE REGULATORS

- \* OUT PUT CURRENT UP TO 1.5 A

- \* OUT PUT VOLTAGESOF 5; 5.2; 6; 8; 8.5; 9;12; 15; 18; 24V

- \* THERMAL OVERLOADPROTECTION

- \* SHORT CIRCUIT PROTECTION

- \* OUTPUT TRANSITION SOA PROTECTION

## V. DTMF IC- LM8870 FEATURES

- Low Power Consumption

- Adjustable Acquisition and Release Times

- Central Office Quality and Performance

- Power-down and Inhibit Modes (-02 only)

- Inexpensive 3.58 MHz Time Base

- Single 5 Volt Power Supply

- Dial Tone Suppression

## VI. APPLICATION

- Telephone switch equipment

- Remote data entry

- Paging systems

- Personal computers

- · Credit card systems

Vol. No.7 Issue 02, July-December 2015

www.arresearchpublication.com

# IJEEE ISSN 2321 - 2055

## VII. DTMF CLOCK CIRCUIT

The internal clock circuit is completed with the addition of a standard 3.579545 MHz television color burst crys-tal. The crystal can be connected to a single M-8870 as shown in the Single - Ended Input Configuration on page 3, or to a series of LM-8870s. As illustrated in the Common Crystal Connection below, a single crystal can be used to connect a series of LM-8870s by cou-pling the oscillator output of each LM-8870 through a 30 pF capacitor to the oscillator input of the next LM-8870.

#### VIII. CONCLUSION

To operate industrial automation using GSM communication through 3G technology. To operate relay in microcontroller through DTMF tone. To generate DTMF signal through mobile key paid.

#### REFERENCES

- [1]. Wikipedia The free encyclopedia

- [2]. http://www.instructables.com/

- [3]. rSchenker, L (1960), "Pushbutton Calling with a Two- Group Voice-Frequency Code", The Bell system technical journal 39 (1): 235–255, ISSN 0005-8580

- [4]. "DTMF Tester", "Electronics For You" Magazine, Edition (June 2003)

- [5]. http://www.alldatasheet.com

- [6]. http://www.datasheet4u.com

- [7]. http://www.datasheetcatalog.com